# AN/UYK-7

TECHNICAL

DESCRIPTION

SPERRY UNIVAC

SPERRY  UNIVAC

# **AN/UYK-7**

TECHNICAL DESCRIPTION

### **RESTRICTIVE NOTICE**

This manual is intended to inform the reader regarding the general construction, operational characteristics, and capabilities of the AN/UYK-7 computer. It should not, however, be considered as an equipment specification, and Univac in no way warrants the accuracy or completeness of the manual for procurement purposes.

| <u>Section</u>                         | <u>Title</u> | <u>Page</u> |

|----------------------------------------|--------------|-------------|

| INTRODUCTION                           |              | 1           |

| Physical Characteristics               |              | 2           |

| Cabinet Structure                      |              | 2           |

| Cabinet Dimensions and Weight          |              | 3           |

| Module Structure                       |              | 4           |

| Power Requirements                     |              | 5           |

| Module Functional Characteristics      |              | 6           |

| HARDWARE CONFIGURATIONS                |              | 9           |

| Maintenance Unit                       |              | 9           |

| Remote Operating Control Unit          |              | 10          |

| Installation                           |              | 10          |

| MAINTAINABILITY                        |              | 13          |

| Maintenance Diagnosis                  |              | 13          |

| Parts Replacement and Commonality      |              | 13          |

| FUNCTIONAL DESCRIPTION                 |              | 14          |

| Main Memory                            |              | 14          |

| Contiguous Addressing                  |              | 14          |

| Interleaved Addressing                 |              | 15          |

| Non-Destructive Read-Out (NDRO) Memory |              | 15          |

| Integrated-Circuit Control Memory      |              | 15          |

| Central Processor                      |              | 16          |

| Executive Control Instructions         |              | 16          |

| Processor Control Memory               |              | 16          |

| Addressable Registers                  |              | 16          |

| Breakpoint Register                    |              | 18          |

| Active Status Register (ASR)           |              | 18          |

| Arithmetic Registers (A)               |              | 18          |

| Base Registers (S)                     |              | 18          |

| Index Registers (B)                    |              | 18          |

| Program Address Register (P)           |              | 18          |

## TABLE OF CONTENTS (CONT.)

| <u>Section</u> | <u>Title</u>                                      | <u>Page</u> |

|----------------|---------------------------------------------------|-------------|

|                |                                                   |             |

|                | Processor Monitor Clock                           | 20          |

|                | Control Section Adders                            | 21          |

|                | Memory Read-Write Lockout                         | 21          |

|                | Control Of Input And Output                       | 21          |

|                | Interrupts                                        | 22          |

|                | Power Tolerance Interrupt                         | 22          |

|                | Interrupt Processing                              | 22          |

|                | Multiple Interrupts                               | 23          |

|                | IOC Interrupts                                    | 23          |

|                | Input-Output Controller and Adapter               | 23          |

|                | Interface Adapter                                 | 24          |

|                | Input-Output Controller Registers                 | 25          |

|                | Real-Time Clock                                   | 25          |

|                | Monitor Clock                                     | 26          |

|                | IOC Commands                                      | 26          |

|                | OPERATIONAL DESCRIPTION                           | 27          |

|                | Processor                                         | 27          |

|                | Instruction Word Formats                          | 27          |

|                | Instruction Address Generation                    | 27          |

|                | Indexing                                          | 29          |

|                | Addressing                                        | 31          |

|                | Repeat Mode                                       | 31          |

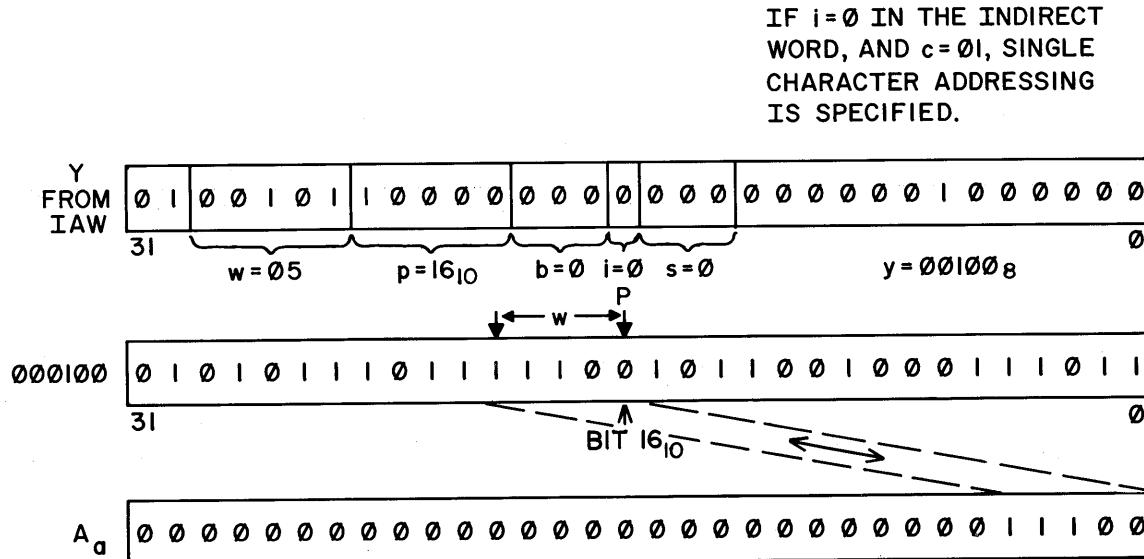

|                | Indirect Addressing                               | 35          |

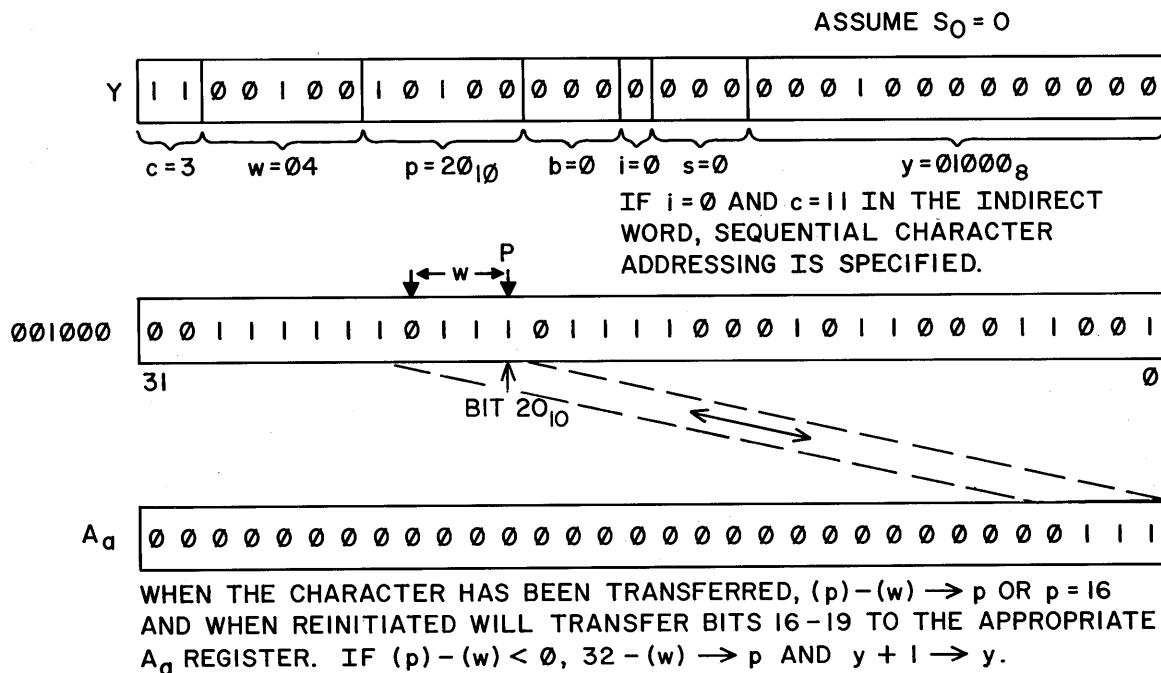

|                | Character Addressing                              | 35          |

|                | Interrupt Code Generation                         | 35          |

|                | Input-Output Controller (IOC)                     | 35          |

|                | Priorities                                        | 35          |

|                | Program Chains                                    | 35          |

|                | Processor-IOC Non-Buffered Requests               | 37          |

|                | Externally Specified Index (ESI) Buffer Transfers | 37          |

|                | Externally Specified Address (ESA) Word Transfers | 38          |

|                | REPERTOIRE OF INSTRUCTIONS                        | 44          |

|                | Conventions and Abbreviations                     | 44          |

|                | Processor                                         | 46          |

|                | Input-Output Controller                           | 67          |

## LIST OF ILLUSTRATIONS

| <u>Figure</u> | <u>Title</u>                                                | <u>Page</u> |

|---------------|-------------------------------------------------------------|-------------|

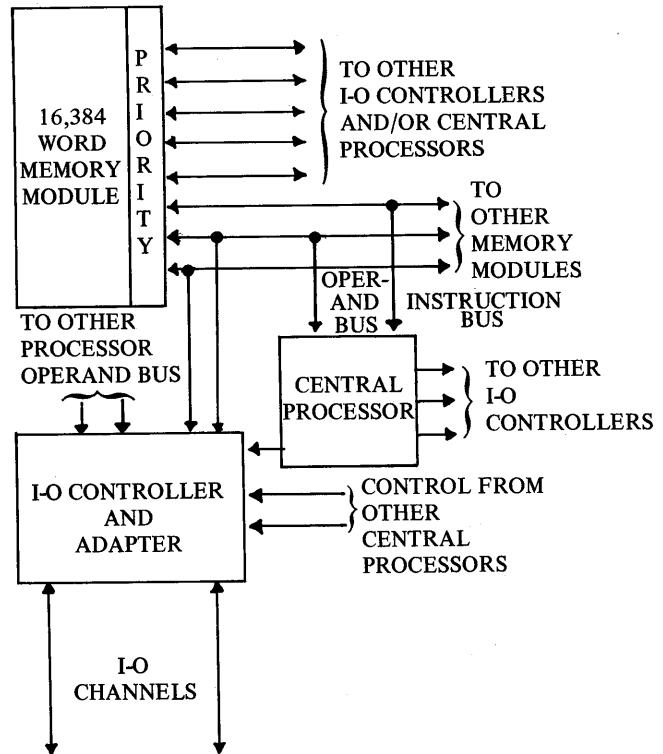

| 1             | AN/UYK-7 Functional Diagram                                 | 2           |

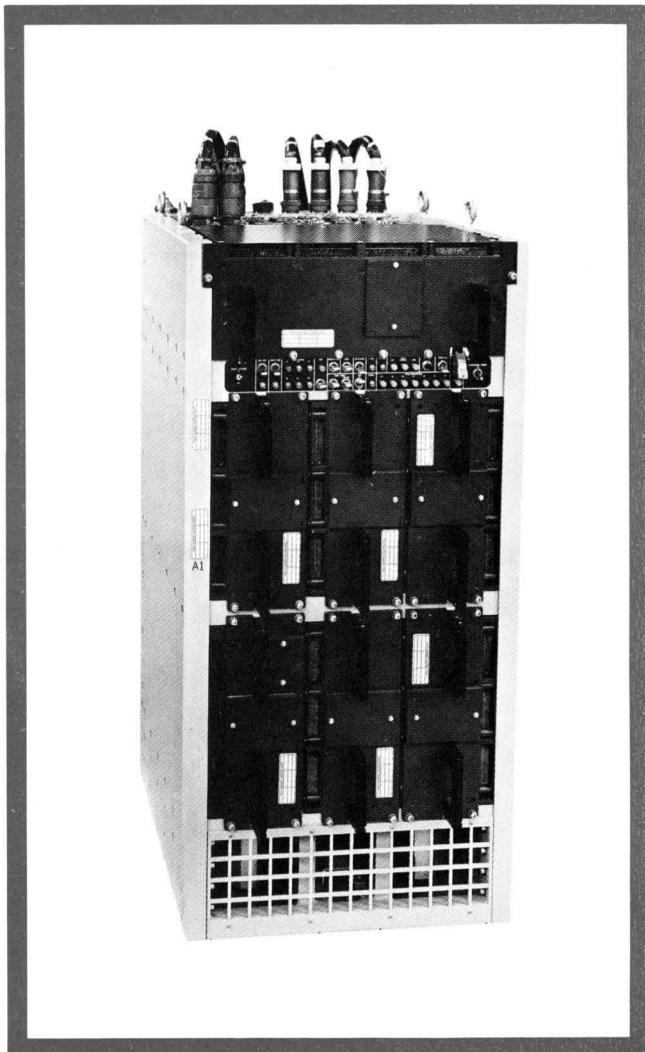

| 2             | UYK-7 Cabinet                                               | 3           |

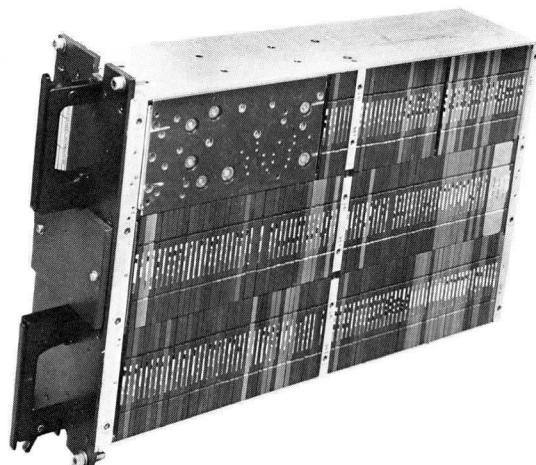

| 3             | Central Processor (Card Side)                               | 4           |

| 4             | Input-Output Adapter (Card Side)                            | 4           |

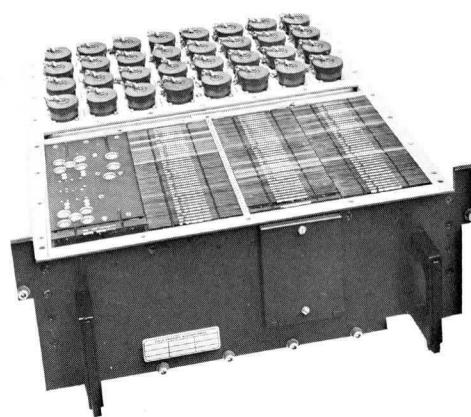

| 5             | Power Supply                                                | 4           |

| 6             | Full Five-Cabinet 3-by-4 Multi-Processor Configuration      | 9           |

| 7             | Maintenance Unit Panel                                      | 10          |

| 8             | Cabinet Installation and Dimensional Diagram                | 11          |

| 9             | Cable and Interface Connections                             | 12          |

| 10            | Printed-Circuit Cards                                       | 13          |

| 11            | Memory Module                                               | 15          |

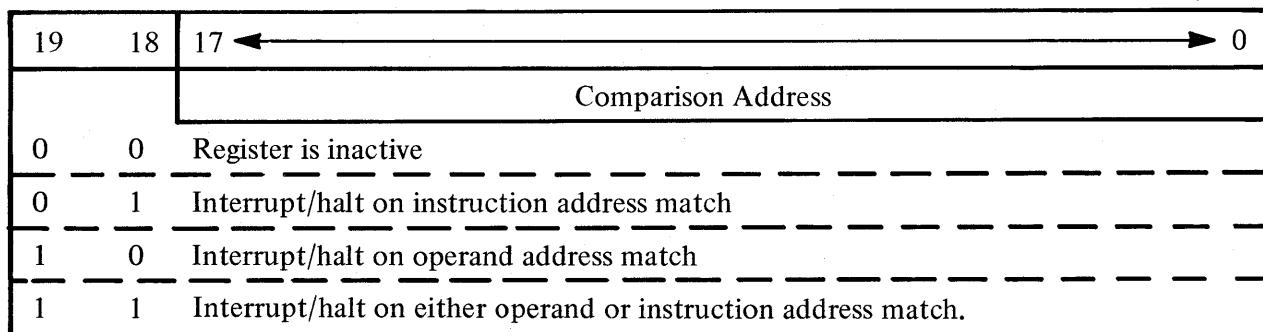

| 12            | Breakpoint Register Format                                  | 17          |

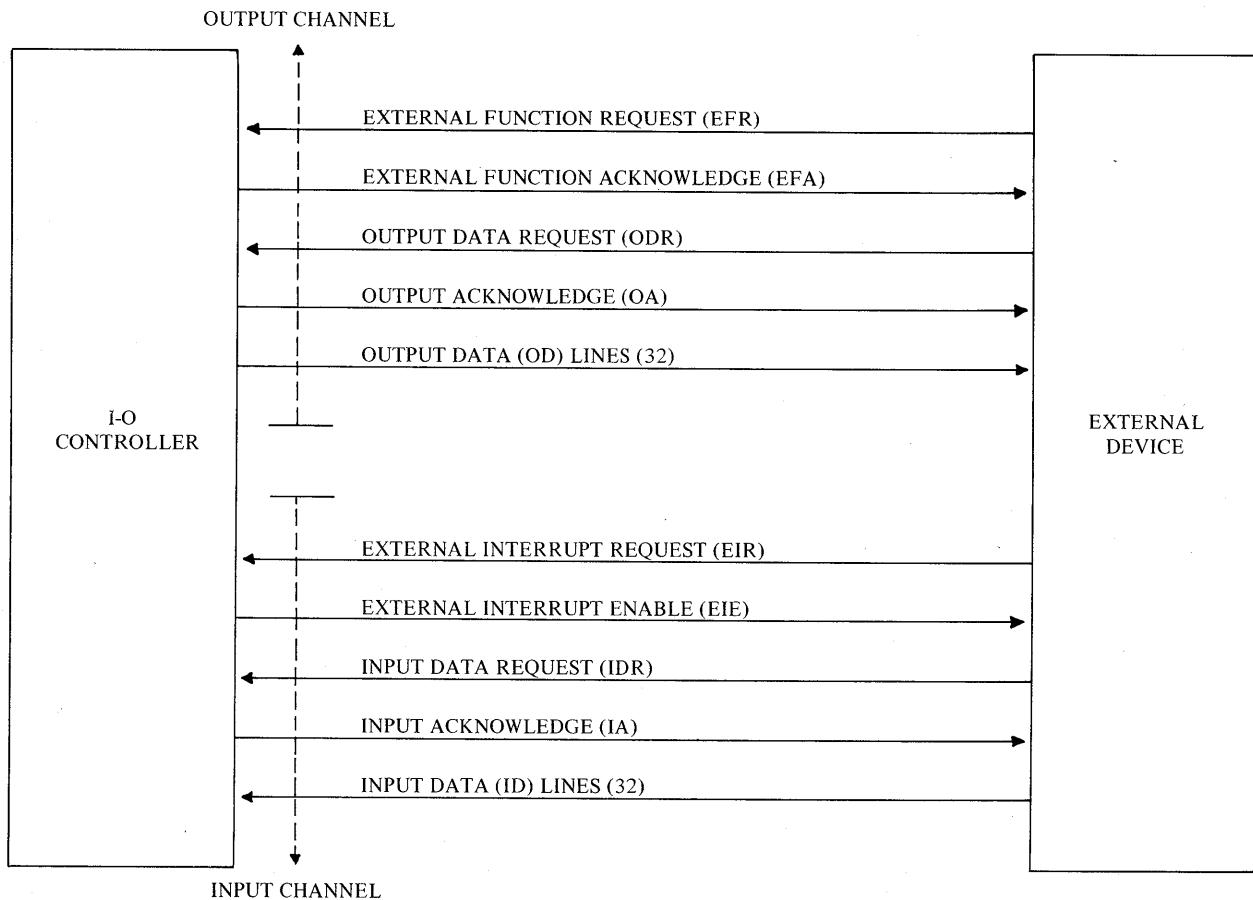

| 13            | I-O Controller-External Device Communication                | 24          |

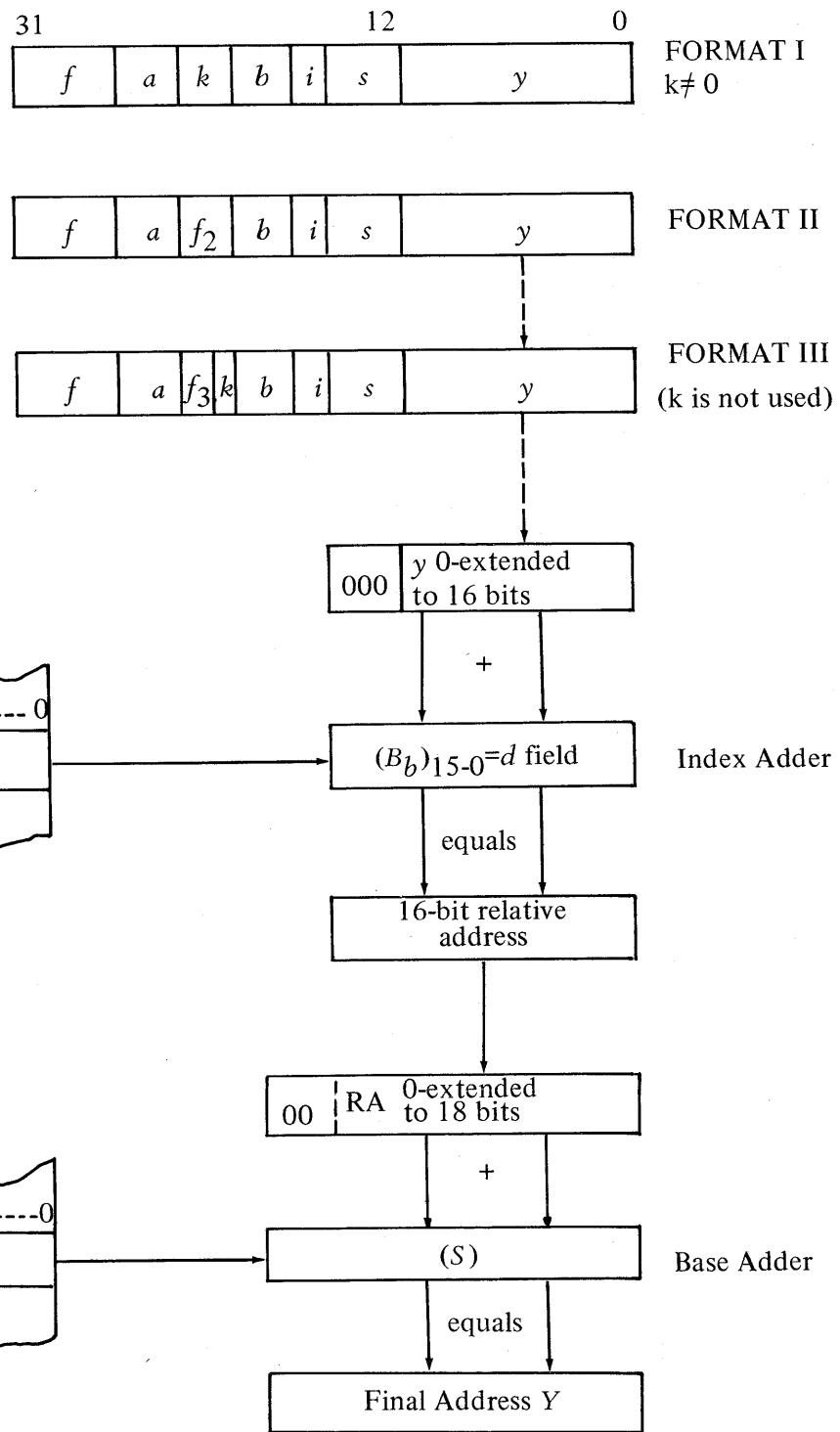

| 14            | Processor Instruction Word, Indirect Address Word Formats   | 28          |

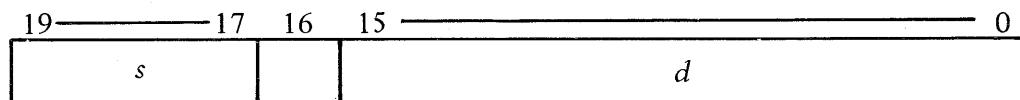

| 15            | Instruction Address Generation                              | 29          |

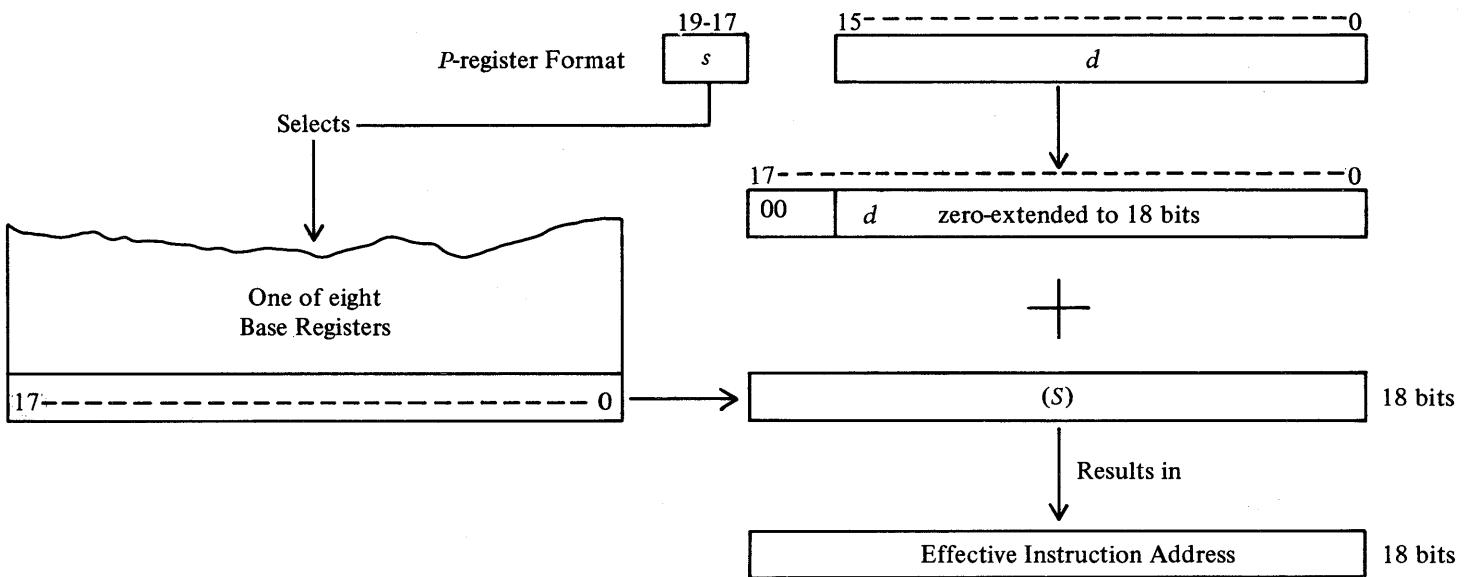

| 16            | P-Register and Index-Register Format                        | 29          |

| 17            | Direct-Address Generation                                   | 32          |

| 18            | Examples of Indirect Addressing                             | 34          |

| 19            | ESI Buffer Control Word Format                              | 38          |

| 20            | Main Memory Buffer Control Word Format                      | 39          |

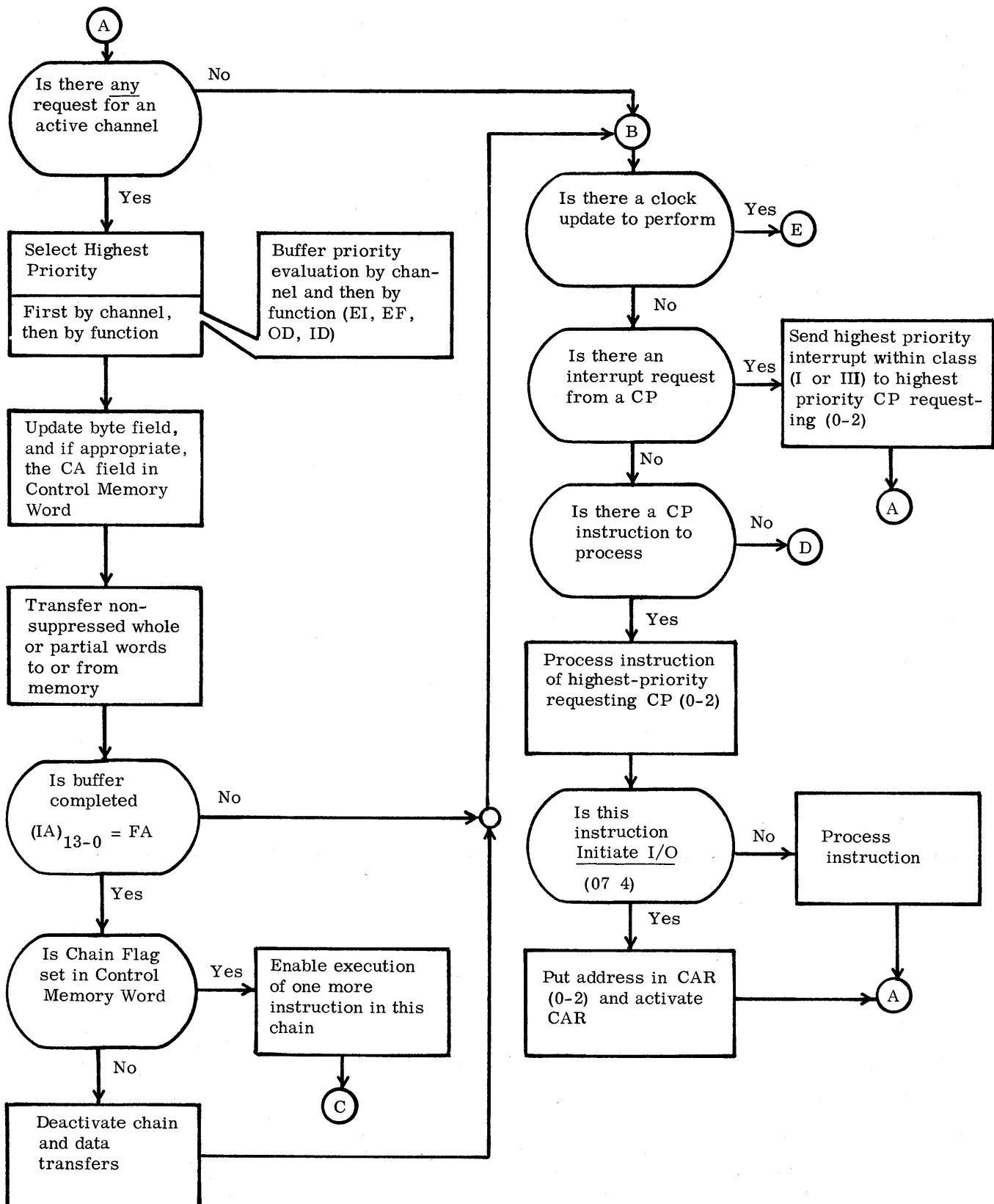

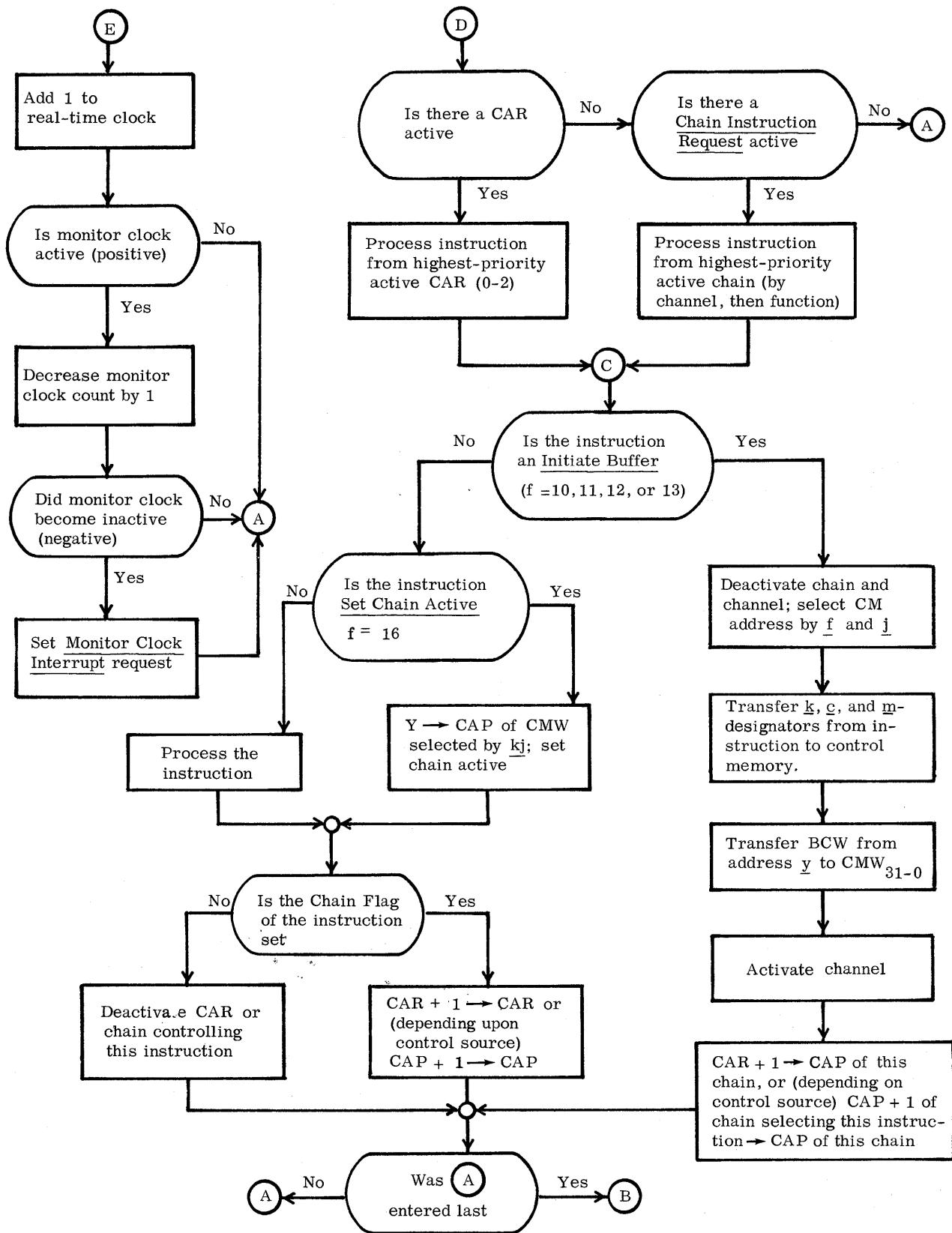

| 21            | Sequences of IOC Processing                                 | 42          |

| 22            | Normalized Floating-Point Word Format                       | 49          |

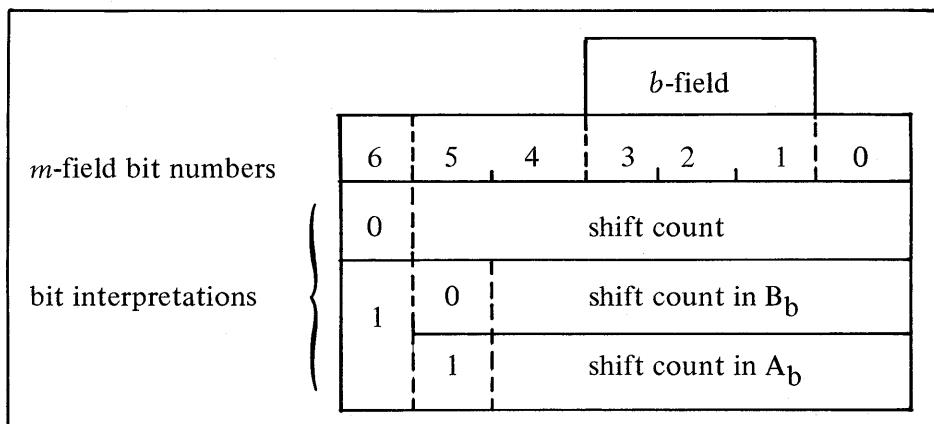

| 23            | m-Field Interpretation for Shift Instructions (codes 62-67) | 63          |

## LIST OF TABLES

| <u>Table</u> | <u>Title</u>                                                                                     | <u>Page</u> |

|--------------|--------------------------------------------------------------------------------------------------|-------------|

| 1            | UYK-7 Module/Element Weight and Size                                                             | 3           |

| 2            | Primary Power Characteristics                                                                    | 5           |

| 3            | Module/Element Power Requirements                                                                | 5           |

| 4            | Central Processor Control Memory Address Assignments                                             | 17          |

| 5            | Active Status Designator                                                                         | 19          |

| 6            | IOC Control Memory Address Assignments                                                           | 25          |

| 7            | Registers Specified By The $a$ , $b$ , And $s$ -Designators                                      | 30          |

| 8            | Format I Instruction $k$ -Field Interpretation                                                   | 30          |

| 9            | Indirect Word Address Generation                                                                 | 33          |

| 10           | Interrupt Status Codes                                                                           | 36          |

| 11           | IOC Control Memory Buffer Control Word Format                                                    | 37          |

| 12           | IOC Command Word Format                                                                          | 39          |

| 13           | $k$ -Field Interpretation: IOC Command Codes 10, 11, & 13<br>And Associated Control Memory Words | 40          |

| 14           | $k$ -Field Interpretation: IOC Command Codes 12, 13, 15, & 16                                    | 40          |

|              | IOC Request Priorities                                                                           | 41          |

| 16           | Storage Protection Format and Examples                                                           | 50          |

UNIVAC® AN/UYK-7 Military Computer

## INTRODUCTION

The AN/UYK-7 computer is a highly reliable, ruggedized multiple-processor system designed and manufactured by the Univac Division of Sperry Rand Corporation for military applications. Advanced design techniques and a versatile functional and physical architectural philosophy provide for efficient and convenient applications across the entire spectrum of military data-processing requirements. The AN/UYK-7 can be assembled to meet small, medium, or large system configuration requirements without sacrificing functional versatility. Logical, independently timed computer modules share functional operations with asynchronous intercommunication in either the small systems, or in those involving complex manipulations of massive amounts of data, in real-time and/or scheduled activities.

Past experience in meeting the stringent environmental and functional specifications imposed on military systems guided Univac engineers in designing the computer to MIL-E-16400 (ship and shore) environmental requirements. Combinations of micro-electronic, monolithic integrated circuits, new logic, and high-density packaging techniques, facilitate application where reduced volume and weight are important considerations. The functional and physical modularity of the system affords a variety of processing and input/output capabilities for immediate and future applications.

The AN/UYK-7 features many next-generation data-processing characteristics. Rapid transfer and partial data-processing are provided in communication between external devices and large internal random-access storage. Unique timing and access priority techniques used with a 1.5-microsecond (read-store cycle) main memory permits operation as several parallel memories, thus increasing computer operating speed. Simultaneous memory references can effectively increase total

memory utilization by a factor of eight in the larger configurations and by a factor of two in the single-processor instruction execution times. This advanced timing feature produces an average command execution time as low as 1.5 microseconds, and an input transfer capability of over one million 32-bit words per second in the smaller AN/UYK-7 configurations.

Specific design studies on efficient executive program operation as encountered in the real-time world revealed desirable features now incorporated in the functioning modules. Separate sets of index, arithmetic and relative address (base) registers are provided so that no processing time is lost in capturing worker-program data when the executive is initiated. A set of 18 privileged instructions with special characteristics for executive control is reserved exclusively for the executive mode. Computer activity is monitored by a dynamic status register that directs computer control and provides the status information when required by executive programs. Enhancing the capability to meet military requirements in processing data is a memory-protect feature under executive control that guards accessibility to classified data. These are among many new and vital features incorporated in the AN/UYK-7 computer for greater systems control and systems utilization.

The AN/UYK-7 is designed to operate as a single processor or as a multiple-processor system. Word lengths of 32 bits facilitate processing for byte-oriented systems as well as for word- or bit-stream-oriented types. A single-cabinet, single-processor configuration can contain up to 48K words of memory and up to 16 input/output channels. It can, by its addressing structure, command additional external memory units containing up to thirteen 16,384-word modules of magnetic core memory. An AN/UYK-7 computer configuration consists of the following modules:

Central processor

Input-output controller

Input-output adapter (4, 8, 12 or 16 channels)

Magnetic core memory (16,384-word)

Power supply

Cabinet with blowers and operating panel

Remote operating control unit

Maintenance console unit

Dummy units for unused module spaces

A minimum system contains one central processor, one input-output controller, one 4-channel input-output adapter, one memory module, and one power supply in a single cabinet. The basic one-cabinet system has three memory modules (48K words), one input-output controller, an I-O adapter with 16 input and 16 output channels, a power supply, and a processor.

Figure 1 is a functional diagram illustrating the intercommunication capabilities among the functional modules, and indicating the variety of possible configurations. Expansion of a minimum or basic system can be performed in the field. Expansion beyond a three-processor, four-input-output-controller system with 262K words of shared memory is a further objective of the design. This can be achieved with other AN/UYK-7 computers, connected to input-output controllers on inter-computer channels, and through the use of shared memory modules. Priority of action is provided to prevent channel interference.

Any channel of an input-output controller can be an inter-computer channel. This characteristic permits one AN/UYK-7 to communicate with one or more other processors or compatible computers, which, in turn, can communicate with their own peripheral devices or other computers. Such a chain configuration of computers and peripheral devices can provide a broad system capability.

## PHYSICAL CHARACTERISTICS

Emphasis on functional and physical modularity in architectural design permits a wide variety of configuration assemblies. Needed amounts of memory storage, processing capability and input/output capacity can be selected as required.

Figure 1. AN/UYK-7 Functional Diagram

Expanding the AN/UYK-7 system to meet additional requirements requires adding only those modules that perform the functions desired. Limits of expansion are determined by the amount of inter-module communication required and the addressing capability of each module. The operational size of an AN/UYK-7 computer system and the required number of cabinets result directly from the number of modules.

## CABINET STRUCTURE

One basic UYK-7 welded aluminum frame cabinet accommodates all modules, including the maintenance panel which may be mounted on top. The cabinet contains module mounting slides and retaining hardware, module electrical connections and interconnecting wiring harness, operating panel, a blower, and a system of air ducts to draw cooling air through all module heat exchangers. Modules slide in from the front to make electrical connections with recepticles terminating the interconnecting harness in the rear. A combination

handle and locking mechanism on the front of each module mates with retaining forks on the cabinet for securing and releasing. This cabinet and module design permits rapid removal and replacement of plug-in modules. Electrical inter-module wiring and power distribution wiring are made accessible by removing the rear panel. The cooling blower is located at the bottom, the operator's panel at a convenient height on front. Figure 2 shows a cabinet with all modules in place.

Power connectors, input/output channel connectors, and interface circuitry are on top.

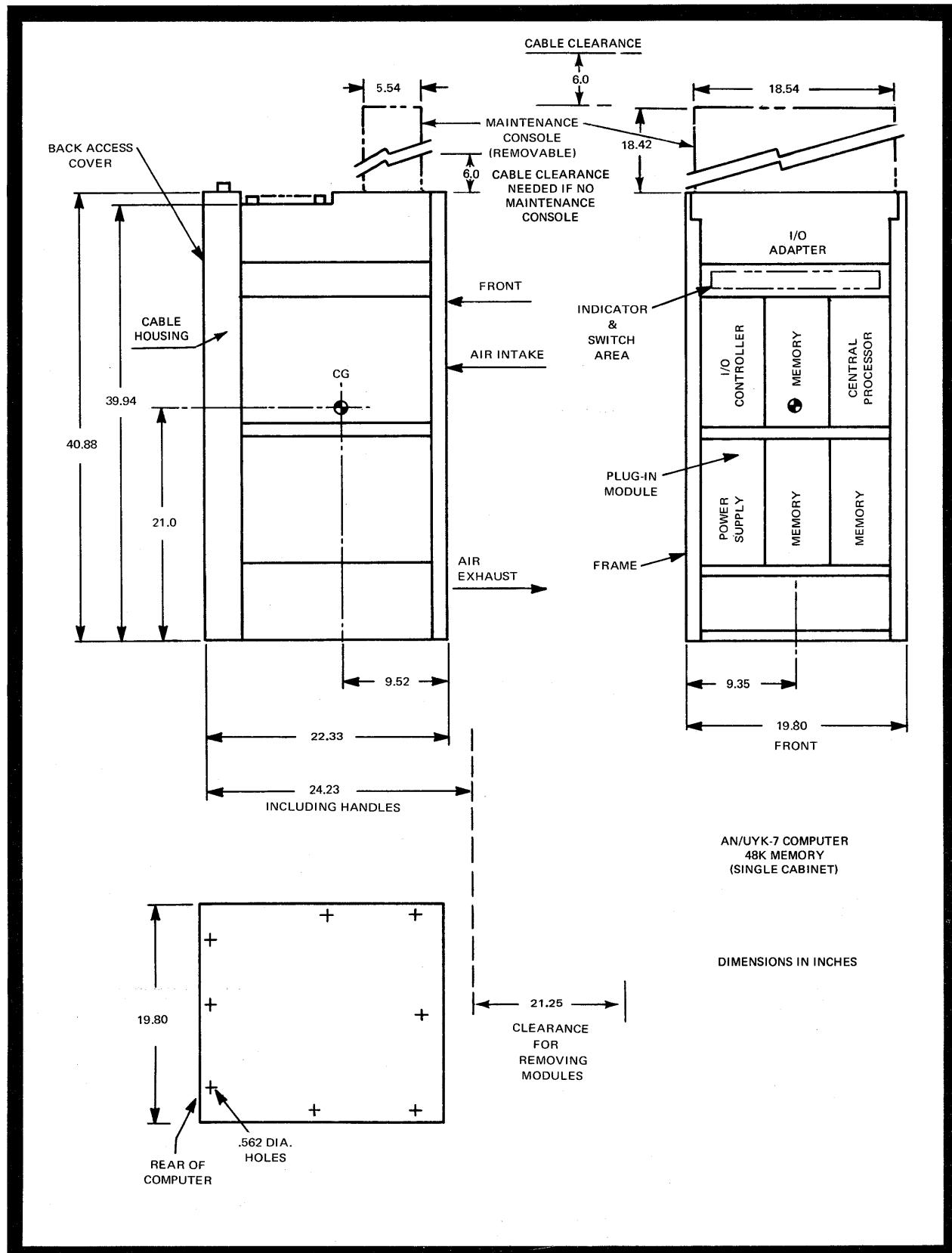

#### CABINET DIMENSIONS AND WEIGHT

The UYK-7 cabinet as illustrated in Figure 2 is 19.80 inches wide, 40.88 inches high and 22.34 inches deep (excluding the module handles); it occupies approximately 10.46 cubic feet. Cabinet depth, including the module handles, is 24.20 inches. The total weight of a UYK-7 computer and the power consumed are based on a specific configuration. When functional modules do not fill a cabinet, dummy units are installed in empty drawer positions to close the space and to rechannel the air flow. Weights and sizes of individual modules and dummy units are listed in Table 1.

The single processor cabinet can pass through an entry 21 inches wide and 42 inches high, or through a 30- by 30-inch hatch.

Figure 2. UYK-7 Cabinet

TABLE 1. UYK-7 MODULE/ELEMENT WEIGHT AND SIZE

| MODULE/ELEMENT             | WEIGHT (POUNDS) | SIZE (INCHES)<br>(excluding handles) |       |       |

|----------------------------|-----------------|--------------------------------------|-------|-------|

|                            |                 | W                                    | H     | D     |

| Central Processor Unit     | 48              | 5.44                                 | 11.35 | 18.44 |

| I-O Controller             | 46.5            | 5.44                                 | 11.35 | 18.44 |

| I-O Adapter                | 50              | 17.92                                | 6.62  | 18.44 |

| Memory Unit                | 47.5            | 5.44                                 | 11.35 | 18.44 |

| Power Supply               | 65              | 5.44                                 | 11.35 | 18.44 |

| Cabinet (including blower) | 169.5           | 19.80                                | 40.88 | 22.34 |

| Dummy Unit (IOC/MU/CO/PS)  | 6 (estimated)   | 5.44                                 | 11.35 | 18.44 |

| Dummy I-O Adapter          | 12 (estimated)  | 17.92                                | 6.62  | 18.44 |

## MODULE STRUCTURE

Modules in the UYK-7 are built with common dimensions wherever possible (Table 1). With the exception of the power supply, each module has a wire-wrapped back panel terminating in receptacles that mate with the male connectors on printed circuit cards and memory modules (all of which are keyed and coded to prevent misinsertion).

All heat dissipated by circuit elements is transferred to the top of the card or memory assembly by thermal conduction to metallic "T" bars.

The assembled module is closed by a heat-exchanger cover that makes thermal contact with all "T" bars. Ambient air, drawn through the exchanger by the cabinet cooling system, removes heat to the outside. Figures 3 and 4 show the central processor and I-O adapter modules with heat exchangers removed.

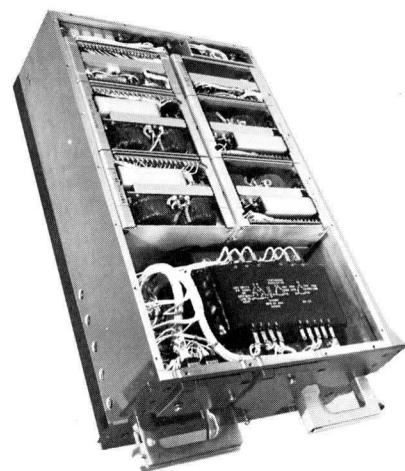

The power supply discrete components and monitoring circuits are removable to facilitate maintenance. Thermal conduction to heat exchangers is also accomplished in these modules. Figure 5 shows the power supply with bottom cover removed.

Figure 3. Central Processor (Card Side)

Figure 4. Input-Output Adapter (Card Side)

Figure 5. Power Supply

## POWER REQUIREMENTS

The computer is designed to operate with primary power input as shown in Table 2. With the aid of appropriate programming, operation through transients that may cause data loss is avoided by design; contents of volatile registers are transferred to main memory via software and retained for

immediate restart of processing after power returns to normal.

Power consumption for different computer configurations may be determined by using the estimates of individual module requirements shown in Table 3.

TABLE 2. PRIMARY POWER CHARACTERISTICS

| PARAMETER                               | REQUIREMENT                                                                 |

|-----------------------------------------|-----------------------------------------------------------------------------|

| Voltage                                 | 115 volts $\pm$ 10% (line-to-line)<br>or 208 volts $\pm$ 10% (line-to-line) |

| Power                                   | 2500 watts (nominal for basic computer)                                     |

| Phases                                  | 3 Delta (115V) or wye (208V)                                                |

| Phase rotation                          | A: B: C                                                                     |

| Frequency                               | 400Hz $\pm$ 5%                                                              |

| Power factor                            | 0.8 lagging (minimum)                                                       |

| Maximum transient voltage and frequency | As specified in MIL-E-16400                                                 |

TABLE 3. MODULE/ELEMENT POWER REQUIREMENTS

| MODULE/ELEMENT                                                | POWER REQUIREMENTS |

|---------------------------------------------------------------|--------------------|

| Power Supply Unit (with load of 1-CP, 1-IOC, 1-IOA, & 1 MU)   | 140 watts          |

| Central Processor Unit (CP)                                   | 460 watts          |

| Input-Output Controller (IOC)                                 | 405 watts          |

| Input-Output Adapter (IOA)                                    | 205 watts          |

| Memory Unit (MU)                                              | 210 watts          |

| Maintenance Console (include PS loading)                      | 70 watts           |

| PS loading per added MU                                       | 23 watts           |

| Power Transformer (with load of 1-CP, 1-IOC, 1-IOA, and 1-MU) | 80 watts           |

| Power Transformer loading per added MU                        | 12 watts           |

| Fans (per main cabinet)                                       | 150 watts          |

## MODULE FUNCTIONAL CHARACTERISTICS

### MEMORY MODULE

Temperature stable coincident-current magnetic core

Capacity: 16,384 32-bit words

Eight access ports per module with priority selection

1.5-microsecond read-write cycle time

Optional interleaved addressing between two modules

### CENTRAL PROCESSOR MODULE

Overlapped operation, two or more memory modules

130 basic whole and half-word instructions

Direct or indirect addressing

Variable length character addressing

Privileged instruction set

Task and interrupt operating states

Two sets of seven index and eight base registers

Two sets of eight addressable accumulators

Decremental monitor clock @ 1024 counts per second

Interface capability

16 memory modules (maximum)

4 I-O controllers (maximum)

NDRO memory 512 words

Initial load programs

Fault analysis and recovery

Hardware diagnostic program

Arithmetic

32-bit parallel, one's-complement, binary

Fixed and floating-point hardware

8, 16, 32 or 64-bit operands

### INPUT-OUTPUT CONTROLLER

Direct-access data transfers to and from a maximum of

16 memory modules

Control by 1, 2, or 3 central processors

Programmed operations with command chaining capability

Repertoire of 15 basic instructions

Integrated-circuit control memory

Buffer control words

Command address pointers (function control fields)

Clock storage

Internal or External Real-Time Clock

1024 count per second (Internal)

Up to 100 kHz (External)

Operating modes

Normal buffer

Externally specified index

Externally specified address

Command chaining

Continuous data mode

Pack and unpack 8, 16 or 32-bit bytes

Inter-computer communication

Interface adapter

4, 8, 12 or 16 full-duplex input and output channels

32-bit parallel or optional bit-serial channels

| Optional Electrical Interface                        |               |             |                 |

|------------------------------------------------------|---------------|-------------|-----------------|

| Interface Voltage Levels<br>in 4 Channel Groups      | N15<br>(-15V) | N3<br>(-3V) | P3.5<br>(+3.5V) |

| Maximum Data Transfer Rate<br>per Second per Channel | 33,000        | 167,000     | 167,000         |

| Bit-serial channel rate: 10 megabits per second      |               |             |                 |

## POWER SUPPLY MODULE

### Capacity:

Power to six computer modules, remote operator's panel

and maintenance console

### Module Protection

Overload, short-circuits or over-temperature

### Power Failure Detection:

Interrupt of central processor

### Energy Storage:

250 microseconds after input power loss

## OPERATOR'S AND MAINTENANCE PANEL

### Maintenance controls, switches and indicators

Up to 15 feet of interconnecting cable

Separate cabinet

## PHYSICAL CHARACTERISTICS

Militarized construction, welded aluminum cabinet with operating panel

Thermal conductive heat removal to air-cooled heat exchangers

Modular design enhances maintainability

Throw-away printed circuit cards

Convenient expansion and configuration modification:

Single-to-multiple-processor expansion

Shared-memory-configuration changes

Increase of input/output channel capacity

Intermix of main memory modules of different speeds

Basic computer configuration:

Power supply, central processor, I/O controller, I/O interface adapter (16 channels) and 3 memory modules (49,152 words) in a single cabinet

| <u>Computer</u>                                                           | <u>Maintenance Panel/Console</u> |

|---------------------------------------------------------------------------|----------------------------------|

| Size: 40.8" H x 19.8" W x 22.3" D                                         | 18.8" H x 18.5" W x 5.5" D       |

| Volume: 10.4 cubic feet                                                   | 1.2 cubic feet                   |

| Weight: 527 pounds                                                        | 35 pounds                        |

| Power consumption: 2500 watts, 115V, 3-phase, 400-Hz,<br>per MIL-STD-761A |                                  |

## SPECIFICATIONS AND STANDARDS USED FOR DESIGN OBJECTIVES

General Construction: MIL-E-16400 (Enclosure, Inclination)

Radio Frequency Interference: MIL-I-16910

Shock: MIL-S-901 Class I Medium Weight

Vibration: MIL-STD-167 Type I

Salt Spray: FED-STD-151 Method 811

Environmental Characteristics:

Temperature Range:

-54°C to +65°C (Operating)

-62°C to +75°C (Storage)

Relative Humidity to 95%

## HARDWARE CONFIGURATIONS

Consideration of power requirements, power distribution, and length of the inter-module communication bus govern the positions, numbers, and types of modules per cabinet. One power supply can serve six functioning modules (one full cabinet); it is installed in the lower left position in every cabinet. Only one input-output controller and associated adapter may be installed in a cabinet; when used, they occupy top cabinet sections. Below the IOA is the local operators' panel. A cabinet may contain only one central processor. Up to five memory modules may be installed in a cabinet if positions are not used by a central processor or input-output controller. Figure 6 illustrates a 3-processor, 4-IOC multi-processor, five-cabinet configuration, with 262K memory.

### MAINTENANCE UNIT

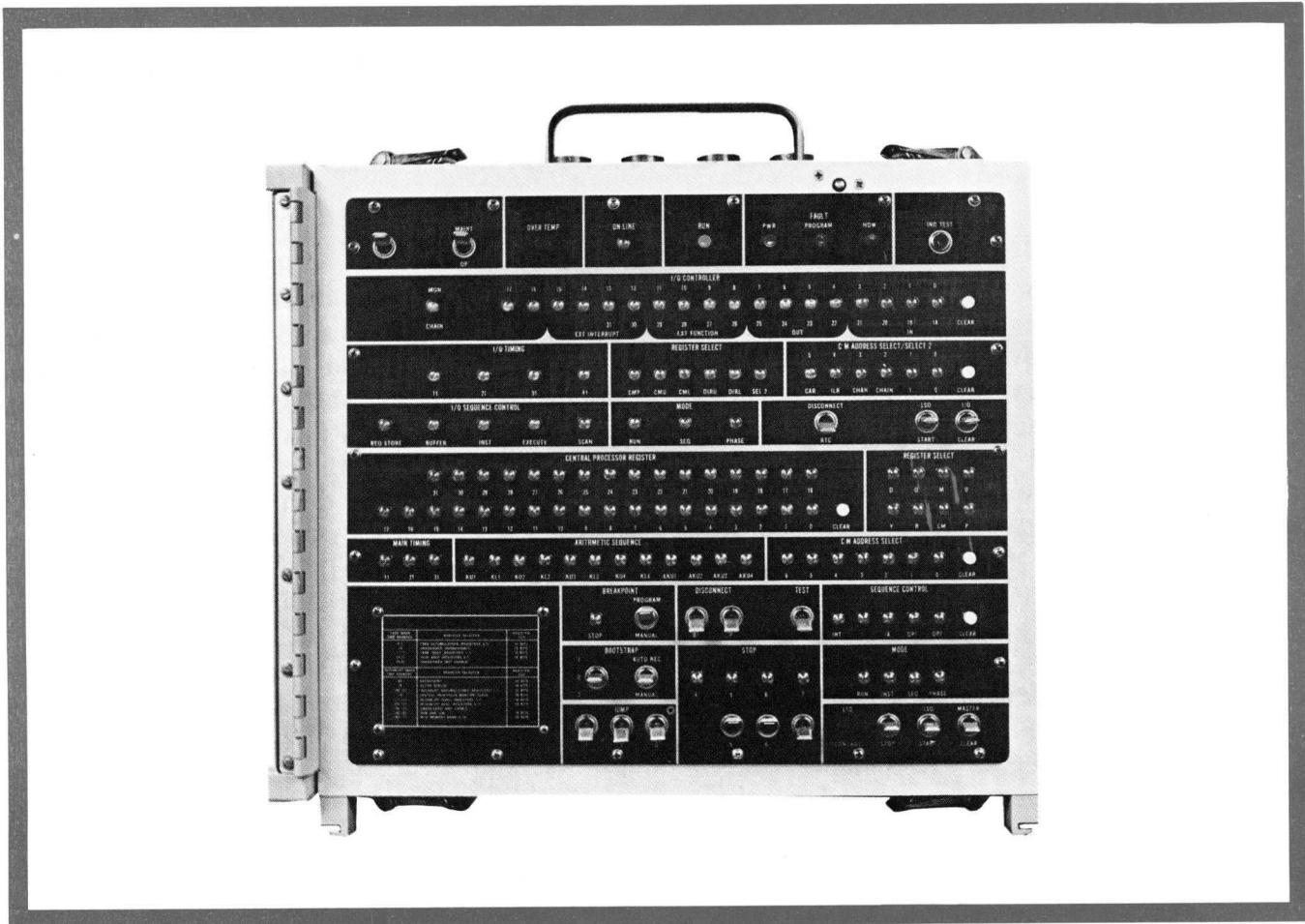

A remote maintenance unit may be placed atop each processor cabinet of the UYK-7, and connected via four cables 15 feet or less in length.

This unit provides operating register displays, processor control displays, and switches for effective operating and maintenance procedures. Computer operation, however, does not require monitoring this unit. Registers are represented on the maintenance unit by rows of pushbutton/indicators, each of which can be used to enter a "1" into a corresponding bit position; and a CLEAR button to enter "0"s into all bit positions in the register. Many of the registers and indicators are involved only in the mechanics of executing instructions and input or output operations. They are not directly applicable to program manipulations, but are provided on the panel as a powerful tool for maintenance.

The maintenance unit is designed and constructed to the same ruggedized requirements as those governing the UYK-7 (Figure 7). This separate unit is contained in a cabinet 18.8 inches high by 18.5 inches wide by 5.5 inches deep, with components accessible from the front. Human engineering

| IOA              |                |                 | DUMMY          |                |                | IOA              |                 |                 | IOA              |                 |                 | IOA              |                       |                       |

|------------------|----------------|-----------------|----------------|----------------|----------------|------------------|-----------------|-----------------|------------------|-----------------|-----------------|------------------|-----------------------|-----------------------|

| OP PANEL         |                |                 | OP PANEL       |                |                | OP PANEL         |                 |                 | OP PANEL         |                 |                 | OP PANEL         |                       |                       |

| IOC <sub>0</sub> | M <sub>2</sub> | CP <sub>0</sub> | M <sub>7</sub> | M <sub>6</sub> | M <sub>5</sub> | IOC <sub>1</sub> | M <sub>10</sub> | CP <sub>1</sub> | IOC <sub>2</sub> | M <sub>13</sub> | CP <sub>2</sub> | IOC <sub>3</sub> | D<br>U<br>M<br>M<br>Y | D<br>U<br>M<br>M<br>Y |

| PS               | M <sub>1</sub> | M <sub>0</sub>  | PS             | M <sub>4</sub> | M <sub>3</sub> | PS               | M <sub>9</sub>  | M <sub>8</sub>  | PS               | M <sub>12</sub> | M <sub>11</sub> | PS               | M <sub>15</sub>       | M <sub>14</sub>       |

4 IOA Modules

5 Operator Panels

4 IOC Modules

3 CP Modules

Memory Modules as required

5 Power Supplies

Memory Modules as required.

By engineering preference, the Central Processor and the Input-Output Controller modules are always located in the upper right and upper left positions, respectively. These positions may alternatively contain Memory Unit modules if the system configuration dictates four or five memory units in a given cabinet. The Power Supply module is always located in the lower left position. In this configuration, not all memory modules are available to every CPU and IOC.

Figure 6. Full Five-Cabinet 3-by-4 Multi-processor Configuration

Figure 7. Maintenance Unit Panel

factors dictated the size and placement of controls used by operator and maintenance personnel. Interface and power cables are connected to the unit through corresponding jacks at the cabinet top.

#### REMOTE OPERATING CONTROL UNIT

A remote operating control unit can be connected to the UYK-7 to permit operational control from up to 300 feet away (total cable length). All necessary power is supplied by the cabinet power supply. Since the system operates mainly under program control, only the minimal but necessary indicators and switches are provided in the remote control panel.

#### INSTALLATION

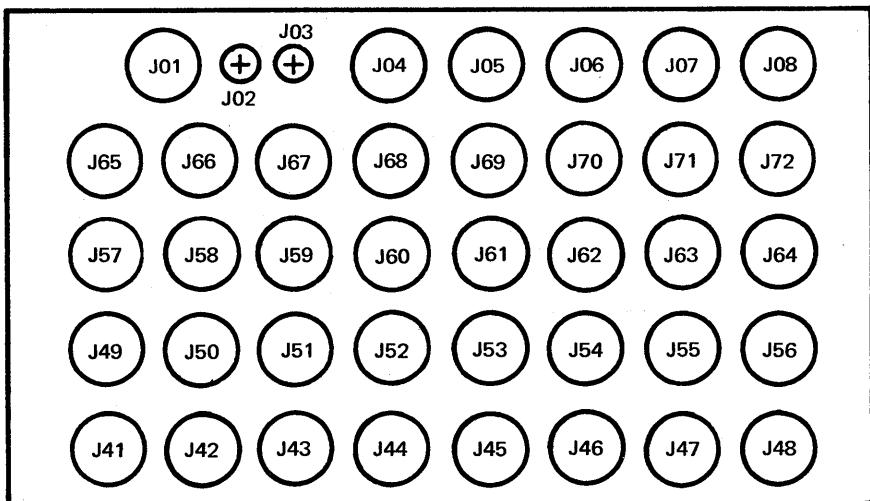

Cabinet design provides front access for module removal and for normal maintenance. The minimum front clearance for module removal is 21.25 inches. Whenever the cabinet installation is subject to mechanical vibration, side and rear clearance of one inch is necessary. Figure 8 shows the dimensions of a single-cabinet installation. A minimum ceiling height of approximately 5.5 feet is required for mounting the maintenance unit, which is 18 inches high, on top of the cabinet during maintenance periods. Cable and interface connections are shown in Figure 9.

Figure 8. Cabinet Installation and Dimensional Diagram

| CONNECTOR<br>REF. DESIG.                                                    | CONNECTOR<br>PART NUMBER          | MATING CONNECTOR<br>PART NUMBER   | FUNCTION                                            |

|-----------------------------------------------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------------------------|

| J01                                                                         | MS 3102R20-15P<br>(905418-04)*    | MS 3106R20-15S<br>(905411-04)     | PRIMARY POWER                                       |

| J05                                                                         | M81511/01E18-85S2<br>(7902701-01) | M81511/06E18-85P2<br>(7902700-01) | CONTROL INDICATE SIGNAL<br>MAINTENANCE CONSOLE UNIT |

| J06                                                                         | M81511/01E18-85S3<br>(7902701-02) | M81511/06E18-85P3<br>(7902700-02) | CONTROL INDICATE SIGNAL<br>MAINTENANCE CONSOLE UNIT |

| J07                                                                         | M81511/01E18-85S4<br>(7902701-03) | M81511/06E18-85P4<br>(7902700-03) | CONTROL INDICATE SIGNAL<br>MAINTENANCE CONSOLE UNIT |

| J08                                                                         | M81511/01E18-85S5<br>(7902701-04) | M81511/06E18-85P5<br>(7902700-04) | CONTROL INDICATE SIGNAL<br>MAINTENANCE CONSOLE UNIT |

| J04                                                                         | M81511/01E18-85S6<br>(7902701-05) | M81511/01E18-85P6<br>(7902700-05) | SYSTEM MONITOR PANEL<br>OR REMOTE OPERATING UNIT    |

| J02                                                                         | MS 3112E8-4S<br>(7900533-00)      | MS 3116F8-4P<br>(7901820-00)      | EXTERNAL CLOCK<br>(INPUT)                           |

| J03                                                                         | MS 3112E8-4S<br>(7900533-00)      | MS 3116F8-4P<br>(7901820-00)      | EXTERNAL CLOCK<br>(OUTPUT)                          |

| J41, 43, 45,<br>47, 49, 51, 53,<br>55, 57, 59, 61,<br>63, 65, 67, 69,<br>71 | M81511/01E18-85P1<br>(7902698-00) | M81511/06E18-85S1<br>(7902699-00) | INPUT CHANNELS                                      |

| J42, 44, 46,<br>48, 50, 52, 54,<br>56, 58, 60, 62,<br>64, 66, 68, 70,<br>72 | M81511/01E18-85P2<br>(7902698-01) | M8155/06E18-85S2<br>(7902699-01)  | OUTPUT CHANNELS                                     |

Figure 9. Cable And Interface Connections

# MAINTAINABILITY

Maintainability considerations are an integral part of the equipment design. Reliability of a unit is a function of the components selected and manufacturing techniques applied. Processes and controls applied during fabrication reflect quality, which, in turn, supports reliability. Therefore, quality, reliability, and maintainability all contribute to the productive service time of a device by increasing the productive time between malfunctions, and by decreasing the time to repair when a malfunction occurs.

Univac applies three important maintainability philosophies to the design of computing equipment:

- Ease of diagnosis

- Ease of parts replacement

- Commonality of replaceable parts

## MAINTENANCE DIAGNOSIS

Design of the UYK-7 permits front access to all printed-circuit card assemblies for direct testing and physical replacement. Each of the four types of logic module contains a wire-wrapped chassis of printed-circuit cards and other related components and connectors. When the module is withdrawn from the cabinet, a removable cold plate cover permits access to all cards and maintenance modules for easy replacement.

The computer system is logically and electrically designed for easy detection of malfunctioning cards or modules through diagnostic maintenance programs, in conjunction with the maintenance unit. Test points at the front of each unit assist diagnosis of malfunctions. Occasionally, standard test equipment is needed to support self-testing philosophies. However, with the diagnostic programs and related documentation, repair by module replacement and the subsequent checkout can normally be accomplished within 15 minutes.

## PARTS REPLACEMENT AND COMMONALITY

The wire-wrapped chassis are assemblies of printed-circuit cards, containing integrated circuits

and associated discrete components, interconnecting jacks, and a local power converter. Figure 10 is a photo of the printed-circuit cards; their dimensions are 3-3/8 by 3-3/8 by 1/4 inches (including a 56-pin connector). Any functional level can be tested by standard test equipment or diagnostic program. Established test procedures can isolate a malfunctioning card which can be removed and replaced by a spare. Larger parts, such as memory modules and power supply components, can be replaced using simple tools. Spare parts lists are compiled with commonality of parts and established failure rates as governing factors.

Figure 10. Printed-Circuit Cards

# FUNCTIONAL DESCRIPTION

When design of functional capability looks to the future rather than to the state of the art, it dictates a division of effort among elements in a computing system, more than a stressing of speed in memories and central processors. Univac design engineers capitalize on this philosophy in the AN/UYK-7 by assigning to its various modules certain specialized tasks involved in the complete processing system.

For instance, the power supply monitors input power and senses possible failure; it monitors power consumed by the individual modules it supplies, and alerts the central processor to any detected abnormalities that could cause data loss. It also provides orderly computer start-up sequences when normal power is resumed after a shut-down. As another example, certain amounts of data preprocessing or format arrangement, buffer control, real-time clock functions, and interrupt procedures are assigned to the input-output controller. And, multiple requests addressed to a memory module at any time are retained and honored in a priority order by memory module priority circuits.

In essence, each functional module in the UYK-7 executes a certain portion of the tasks that normally have been performed by a central processor.

## MAIN MEMORY

Main memory is composed of modules (banks) of random access, coincident-current destructive-readout core storage with a read-restore cycle of 1.5 microseconds. Each main memory module contains four core stacks, a power converter, address translation, and timing and control circuitry. Minimum memory for a computing system is one module. However, each central processor or input-output controller can address up to 262K words or 16 modules.

Eight interfacing paths (one bus and one port for each path), allowing access to memory, are provided in a 16 K-word module for

communication with other modules. Separate paths are used by the processor for storing and receiving data and for extracting instructions from storage. The interfaces are served in a priority order if simultaneous requests are presented. The order of priority is fixed at the time the interconnecting bus harness is manufactured. It, therefore, must be assigned, as desired, in the ordering document.

Ready and resume logic permits asynchronous operation with the processors and input-output controllers. Each bus that connects a memory port to the input-output controller or to the processor carries the service request and associated operand, or instruction address and the requested operands or instructions. For a specific memory reference the user (processor or input-output controller) presents a request signal and an address to memory on the interface bus. The memory module, identified by the user, responds to the request (read, write or read-and-write) when in the ready state and performs the function. Operands or instructions thus transferred are carried on the same bus as the respective addresses and requests. Sequencing and traffic direction on all busses connected to a memory module are controlled by the timing circuitry, the ready-resume logic and the priority network. When the module is not in the ready state at a particular port, any request on that port is held in the priority network for its ordered turn. This asynchronous operating philosophy permits as many read, write or read and write references to progress at any instant as there are memory modules in the system.

## Contiguous Addressing

All memory modules with contiguous addressing contain addresses 00000 through 37777<sub>8</sub>. Address translators interpret a 14-bit portion of an 18-bit address furnished by the user to select a word within an addressed module. Each such module responds to requests when the value on the selection lines corresponds to the number assigned to that module in the system.

Figure 11. Memory Module

### Interleaved Addressing

The UYK-7 memory system can be modified (an option) for interleaved addressing by module pairs (32K words of memory). In this configuration, the even-numbered addresses in the range 00000 through 77776 are accepted and translated by the even-numbered module of the pair, and the odd-numbered addresses in the range 00001 through 77777 are accepted and translated by the odd-numbered module of the pair.

### NON-DESTRUCTIVE READ-OUT (NDRO) MEMORY

Each processor contains a 512-word assembly of NDRO magnetic core rope memory containing the hardware interrupt analysis routine, two initial load or automatic recovery routines (bootstrap), and a diagnostic program. If desired, one long,

more sophisticated routine can be located in these addresses; however, the programs must be selected at the time of manufacture. The NDRO memory is separated from the total addressing continuum of main memory; the memory used (NDRO or main) depends upon the operating state and operator's panel switch positions.

Hardware error interrupts, when enabled, force the processor into the hardware interrupt analysis routine for diagnosis and transfer to remedial action or stop. NDRO routines have several entries. According to conditions causing the entries, an NDRO routine may exit to another routine or come to an orderly stop. ("Interrupt Processing" has further details.)

### INTEGRATED-CIRCUIT CONTROL MEMORY

Each processor and input-output controller is equipped with a fast integrated-circuit memory

used during the execution of instructions and input or output transfers, to capture, maintain, and provide status information when needed; and to provide various controlling addresses and data as dictated by the operating programs. Cycle time is designed to provide accessibility of stored data at precise clock phases so that no time is lost in executing the operating sequences.

## CENTRAL PROCESSOR

The central processor contains all the control, arithmetic and timing circuitry required for processing alpha-numeric data and for executive functions. These include all communication links with other modules under its control or within its sphere of direct influence.

Each central processor can address 262,114 words in 16 memory modules via two busses: one for instructions, and one for operands. In a two- or three-processor system, each processor may (but need not) be connected to all memory modules and input-output controllers; some isolation can be attained by not utilizing all intercommunication capabilities.

Central processors operate in two different modes or states; the Interrupt State executes the executive-type functions, and the Task State processes the worker programs. For convenience and increased response, a separate set of 7 index (B), 8 base (S), and 8 arithmetic accumulator (A) registers is available to the processor in the Interrupt State. This feature precludes the need for storing and restoring register resident data when leaving the Task State and returning. Other control memory registers become functional for the Interrupt State as assigned.

### Executive Control Instructions

The multiple-processing and multi-programming capabilities of the UYK-7 system are enhanced by 16 privileged instructions which permit executive control of the operating system. These instructions, set aside for the exclusive use of the processor in the Interrupt State, include input or output transfer initiation, read and control of the monitor clock, and control of the various processing activities in both the Task and Interrupt

States. If a program in the Task State (a worker program) tries to execute an executive privileged instruction, the worker routine will be interrupted and control transferred to a pre-assigned interrupt entrance address under executive jurisdiction.

Upon receiving an interrupt, program control, through instruction execution or by computer hardware, activates the Interrupt (also called "Executive") State. Either sequence sets the associated interrupt class lockout (described later), stores vital information in associated control memory locations for orderly return to the interrupted program, resets the Program Address (P) Register to the appropriate subroutine entrance address, and effects entry into the Interrupt State. Operations restricted to the Interrupt State generally involve these:

1. Manipulating the Active Status Register

2. Communicating with the input-output controllers

3. Activating the Breakpoint Register

4. Defining memory lockout functions and protected block sizes for worker programs.

5. Reading and activating the monitor clock

6. Interrupt processing

7. Maintaining inter-processor timing compatibility

### Processor Control Memory

Eighty-two integrated-circuit random-access registers of appropriate size serve as the central processor control memory. The various registers are grouped into stacks according to their use, addressing, and relative size.

Access time for each stack varies according to the processor control and arithmetic section timing requirements. Addresses assigned to the various control memory registers are given in Table 4.

### Addressable Registers

Addressable and non-addressable registers enter into the logical execution of all instructions and timing operations in the UYK-7. This functional description is concerned only with those addressable registers involved in operation and programming.

TABLE 4. CENTRAL PROCESSOR CONTROL MEMORY ADDRESS ASSIGNMENTS

| CMR Address | Task State Assignment                                         | Register Size (bits) |

|-------------|---------------------------------------------------------------|----------------------|

| 0 - 7       | Arithmetic Accumulator Registers 0 - 7                        | 32                   |

| 10          | Unassigned (Addressable)                                      | 19                   |

| 11 - 17     | Index Registers 1 - 7 (B)                                     | 19                   |

| 20 - 27     | Base Registers 0 - 7 (S) (addressable in interrupt mode only) | 18                   |

| 30 - 57     | Unassigned (Not useable)                                      |                      |

| CMR Address | Interrupt State Assignment                                    | Register Size (bits) |

| 6X          | Breakpoint (addressable in interrupt mode only)               | 20                   |

| 7X          | Active Status (addressable in interrupt mode only)            | 23                   |

| 100 - 107   | Arithmetic Accumulator Registers 0 - 7                        | 32                   |

| 110         | Central Processor Monitor Clock                               | 19<br>(16-bit clock) |

| 111 - 117   | Index Registers 1 - 7 (B)                                     | 19                   |

| 120 - 127   | Base Registers 0 - 7 (S)                                      | 18                   |

| 130 - 137   | Unassigned (Not useable)                                      |                      |

| 140 - 157   | Designator Storage Words (DSW), Initial Condition Words (ICW) | 20                   |

| 160 - 167   | Storage Protection Registers (SPR) 0 - 7                      | 21                   |

| 170 - 177   | Segment Identification Registers (SIR) 0 - 7                  | 21                   |

Figure 12. Breakpoint Register Format

**Breakpoint Register** — The Breakpoint Register contains 20 bits: 18 bits for a comparison address, and two control bits to designate action to follow a matching comparison. The breakpoint function is implemented by loading control memory register address 6X. Then, a comparison is made between the contents of the Breakpoint Register and the address of each instruction and/or operand, as designated by the control bits. If the PROGRAM/MANUAL switch is in the PROGRAM position and a match is made, the computer sets the *Breakpoint Match* interrupt and transfers the program to the Breakpoint Match Interrupt Entrance address stored in Initial Condition Word 2 (ICW2). If the switch is in the MANUAL position and equality is detected, the computer will halt. Breakpoint word format and the interpretation of elements are shown in Figure 12.

**Active Status Register (ASR)** — The 23-bit status register controls and indicates the status of various operations in a processor. Individual bits and groups of bits are assigned special function as shown in Table 5. If a bit assigned to a function is set, that particular state or function exists and the processor is controlled accordingly. When an interrupt condition is encountered the register contents are stored in control memory before the interrupt state is entered. The interrupt routine can then interrogate and/or change certain bits as required, after which it can return to the interrupted program in a normalized condition. Except for bits 22-15, which are hard-wired, the ASR can be changed by executing the *Load CMR* (Control Memory Register) instructions (codes 54 and 61 with  $i = 0$ ), and selective bits can be changed by the following:

| <u>Instruction</u>                  | <u>Code</u>                   |

|-------------------------------------|-------------------------------|

| <i>Jump on no overflow</i>          | 53 0; $a = 0$                 |

| <i>Jump on overflow</i>             | 53 0; $a = 1$                 |

| <i>Prevent Class III Interrupts</i> | 77 4                          |

| <i>Allow Class III Interrupts</i>   | 77 5                          |

| <i>Compare (arithmetic)</i>         | 42 thru 47<br>and 74 4 - 74 7 |

**Arithmetic Registers (A)** — Two sets of eight arithmetic accumulators (32 bits each) are provided in the processor control memory for

flexible and efficient execution of arithmetic processes. One set is reserved for the Task State and one for the Interrupt State. Bit 10 of the Active Status Register selects the A-register set (along with the index register set). Each instruction defining an operation involving an arithmetic register selects its own accumulator (or pair of accumulators for double-length operations).

**Base Registers (S)** — Two sets of eight, 18-bit base registers, one for the Task State and one for the Interrupt State, are contained in the control memory for final operand and instruction address generation. The Task set is also used for initial-word address definition in the Task State memory lockout function.

A relative addressing philosophy is exercised in the central processor. The instruction furnishes a displacement address that may be indexed by one of seven index registers to form a relative address. The final effective *operand* address is formed by adding the contents of a specified base register to this relative address. The final *instruction* address is formed by adding the contents of the base register defined by the upper three bits of the Program Address Register to the relative address in the lower 16 bits.

**Index Registers (B)** — Two groups of seven 19-bit index registers are provided in control memory for each processor. Bit 10 of the Active Status Register selects the B-index group that operates in the Task or the Interrupt State. One group is assigned to each state so that no interference or delay is encountered during a change from one to the other. For indexing purposes, the lower-order 16 bits of the specified B-register are added to the zero-extended operand address field in the instruction; the upper three bits are not used. Special uses and functional details of the index registers are defined in the particular feature or instruction description.

**Program Address Register (P)** — The 20-bit Program Address Register has 19 bits which are active and one (bit 16), inactive. The three most-significant bits identify one of the eight base registers from the group with which the computer is operating and the lower 16 bits contain the relative address of the next instruction. The lower field count is increased by one, in preparation for

TABLE 5. ACTIVE STATUS DESIGNATOR

|        |         |    |    |    |    |    |    |    |    |    |    |   |   |   |       |   |   |   |   |

|--------|---------|----|----|----|----|----|----|----|----|----|----|---|---|---|-------|---|---|---|---|

| FORMAT | 22 — 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 — 4 | 3 | 2 | 1 | 0 |

|--------|---------|----|----|----|----|----|----|----|----|----|----|---|---|---|-------|---|---|---|---|

| Bit No. | Significance                                                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-20   | Central Processor Identification: individual bits set or cleared permanently by fixed wiring option at time of manufacture.                                |

| 19      | State I                                                                                                                                                    |

| 18      | State II                                                                                                                                                   |

| 17      | State III                                                                                                                                                  |

| 16      | State IV                                                                                                                                                   |

| 15      | Upper/Lower indicator: Set when an upper half-word instruction has been executed; cleared when a whole or lower half-word instruction has been executed.   |

| 14      | Class I Lockout: Set when entering Class I Interrupt State. Locks out Class I interrupts except Power Tolerance interrupt.                                 |

| 13      | Class II Lockout: Set when entering Class I or Class II Interrupt State. Locks out Class II interrupts.                                                    |

| 12      | Class III Lockout: Set when entering Class I, Class II or Class III Interrupt State. Locks out Class III interrupts.                                       |

| 11      | Base register select: Set when entering Interrupt State. Selects base register sets for respective states.                                                 |

| 10      | Accumulator/Index register select: Set when entering Interrupt State. Selects A & B register sets for respective states.                                   |

| 9       | MLO Disable: Set when entering Interrupt State, thereby removing memory lockouts.                                                                          |

| 8       | Load Base Enable: Set by program to allow use of Load Task Register instruction (Code 05 4) in the Task State. Otherwise 05 4 is a privileged instruction. |

\*Analogous to Interrupt classes, which are defined later.

TABLE 5. (Continued)

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Bootstrap Mode: Set by interrupt mode (Class II CP illegal instruction) if AUTO REC/MANUAL switch is in AUTO REC (automatic recovery) position.<br>Set in MANUAL position by the operator.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6-4 | Programmable spare bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3   | Fixed-point overflow: set when a fixed-point overflow condition occurs from those conditions: <ul style="list-style-type: none"> <li>a) Addition: Addend and augend have like signs and the sum has a different sign.</li> <li>b) Subtraction: Minuend and subtrahend have different signs and the difference has a sign different from the minuend.</li> <li>c) Division: Attempt to divide by zero or if the magnitude of divisor times <math>2^{31}</math> is less than the magnitude of the dividend.</li> <li>d) Square Root: Attempt to take square root of a negative number or a number greater than or equal to <math>2^{62}</math>.</li> </ul> |

| 2   | Compare designator: 1 = Equal<br>0 = Unequal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1   | Compare designator: 1 = Greater than or equal<br>0 = Less than                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0   | Compare designator: 1 = Outside of limits<br>0 = Within limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

the next instruction address, each time an instruction is executed.

Either or both fields can be changed when a transfer to another routine is effected. The P-register can be entered manually at the maintenance unit or by program control via jump instructions. When an interrupt is processed, control hardware transfers the address from and to the P-register.

**Processor Monitor Clock** — A 16-bit control memory register can be activated to decrease its count at the rate of 1024 counts per second ( $\pm 2$

counts in 10 seconds) from a positive value loaded by the *Load CMR* instruction. When the count passes through zero, a Class II interrupt (described later) is generated and the decremental process is terminated. Any negative value entered into this Monitor Clock Register will disable the monitor clock. As the interrupt is honored, control is transferred to the program whose entrance address is stored in the control memory register labeled ICW2.

Implementing the external clock option does not change the operation of the monitor clock in the central processor because a separate oscillator module is used in the processor.

## Control Section Adders

Two arithmetic adders take part in the operations involved in instruction execution. Various fields from the instruction register and addressable registers must be interpreted and their functional definitions combined to form address and arithmetic operands:

1. A 16-bit one's-complement index adder updates index counters, advances the relative address field in the P-register, forms partial operand addresses and forms literal operands for the arithmetic section when an instruction defines such operands. Results transferred in the latter case are zero-extended to 32 bits in the arithmetic section.

2. An 18-bit two's-complement base adder forms the effective (final) address of both instructions and operands. Values combined in the base adder are supplied by the index adder and specified base registers.

Values supplied to these adders containing fewer bits than the adder are zero-extended to form a full adder word and then combined with the second input value for the final sum.

## Memory Read - Write Lockout

Worker programs may be prevented access to certain segments of main memory via the memory lockout feature. Any processor, in the Interrupt State, can lock out from its own non-executive operating programs read and/or write operations in defined areas of any memory module. The lockout feature is disabled when the processor reverts to the Interrupt State, and all memory locations become available to the Executive program. If a program in another processor desires the same lockout capability applied to selected areas, its lockout functions must be similarly defined.

Three groups of associated Control Memory Registers govern memory lockout functions. For any block in memory, which may be any size up to 65K words, there are these control activities:

- A base register holds the beginning address definition

- An associated storage protection register

(SPR) defines the lockout function and block size (displacement: number of words, less one)

- A segment identification register (SIR) contains the relative address of the segment identifier (that address in main memory from which the lockout information is transferred)

Table 4 shows control memory assignments and word size. The *Load Base and Memory Protection* instruction (Code 05 4) is programmed to load the base register and its associated SPR from two consecutive memory locations and to save the relative address of the first in the associated SIR.

Memory protection applied to a segment of memory defined by a base register and its associated SPR governs the following operations in the task state:

1. Within the protected area

- prevent or allow reading operands

- prevent or allow storing operands

- prevent or allow executing instructions

- prevent or allow indirect addressing

2. Outside of the protected area

- prevent any operand references

- prevent executing instructions

3. Prevent or allow the use of the Interrupt set of index or base registers for indirect addressing.

If memory protection integrity is to be maintained, each processor must be programmed in terms of the current status of the system. The following programming considerations should be kept in mind:

1. A locked-out area for one processor can be utilized freely by another processor;

2. An active input-output controller can communicate with a locked-out area defined by any processor.

## Control Of Input And Output

Input and output transfers are controlled completely by the input-output controller module addressed by a central processor. I-O command chains are stored in a memory module accessible to the controller for execution. The central processor executes an *Initiate I/O* instruction (code 07 4, a

privileged instruction) which identifies the controller (one of four possible) and the address of the first command in the input/output program sequence. The addressed controller receives an absolute address on the memory-processor operand bus, which is also connected to the controller. Subsequent activity and details are directed by the program available to the controller.

## Interrupts

The UYK-7 processes data from multiple sources in real-time (as events occur) or as scheduled. This ability to process data "on demand" and continue other processing and scheduled operations is implemented by a well-organized interrupt capability.

Interrupts may originate at some remote external device, or they may originate within the computer. Since more than one may occur at the same time, the processor has a priority network with decision-making qualities so it can select the program routine for solving the problem requiring the most urgent attention. Under program control, the other interrupts may be honored in turn according to the next-highest priority, or they may be ignored. Thus, real-time problem solution and maximum processing potential of the system are realized, because less-important routines can occupy the processor's surplus time.

The interrupts in the UYK-7 are processed by an Executive-type program when the central processor is in the Interrupt State. Four classes (Table 5) divide all types into an orderly arrangement to permit selective processing according to importance or timing. Those in Class I are fault and hardware interrupts, including the *Power Tolerance Interrupt* which is never disabled. Class II includes program faults and error interrupts. Grouped in Class III are input and output program faults, program-imposed monitors on input and output transfers, and the *IOC Monitor Clock Interrupt*. The Class IV interrupt is a program-initiated entrance (Instruction Code 07 0) to the Interrupt State. When an interrupt is honored in any class, entrance into the Interrupt State disables all others in that class and also the classes having higher numbers, meaning lower priority.

**Power Tolerance Interrupt** — The power supply contains a feature that protects memory from transferring what may be defective data during primary power interruptions. However, if external sources are attempting data transfers to memory during this protected time, these data may be lost at the input interface. Conditions of both complete power failure, and of power decrease-and-recovery, are resolved without operator intervention if desired.

An interrupt is generated when power falls below a tolerable level. At this time, the computer can still operate for 250 microseconds on residual power stored in the power supply.

When a *Power Tolerance Interrupt* is generated, a program transfer is effected to the address stored in Initial Condition Word 1 (ICW1), and the Class I interrupt lock-out circuitry is set. The routine thus entered has 250 microseconds to store volatile register data. At this point in the routine, a *Manual Jump Instruction* (code 53 3) will have been programmed as a transfer to the restart routine. Design characteristics of this specific jump instruction prevent its execution at below-voltage-tolerance level. Since the voltage level is below tolerance, central processor memory requests and interrupt scans are inhibited.

Depending upon the length and severity of the power problem, two alternatives exist:

1. If power returns to normal before the failure level is reached, the jump is executed and the orderly restart is effected.

2. If the power falls to the failure level, an automatic computer MASTER CLEAR signal is generated by the power supply. Return to normal power, after the computer is cleared, will cause automatic start from the last address in NDRO if the AUTO-START switch is in the AUTO-START position, but will require operator intervention to start if the switch is in the down position.

**Interrupt Processing** — When honoring an interrupt, the processor will store in the Designator Storage Word (DSW) location these current values:

1. The contents of the Program Address (P) Register;

2. The contents of the Active Status Register (ASR);

3. The processor-formed, and/or input-output-controller-formed interrupt status code.

The current ASR will then be changed to reflect the new status, showing:

- appropriate Interrupt State class

- "interrupt" set of accumulator, base, and index registers

- setting of interrupt class lockouts

- removal of the memory lockout

- clearing of overflow and compare designators

- setting of bootstrap designator (if the interrupt is a Class I hardware fault; or if it is Class II and the AUTO REC/MANUAL switch is in the AUTO REC position and the processor is in the Interrupt State, and there is a *CP Illegal Instruction* Interrupt).

Interrupts occurring synchronously with central processor operations are not held pending if they are locked out. These include all Class II interrupts except *CP Monitor Clock* and *Interprocessor Interrupt*; and all in Class I, except *IOC-Memory Resume* and *Intercomputer Time-Out*.

All others, occurring asynchronously with central processor operations, are held pending so the processor can detect them during an instruction priority scan sequence. After the initialization process is completed, the program address is reset in P from the class-associated Initial Condition Word (ICW) in control memory to either the entrance address of the interrupt subroutine or to a bootstrap entrance address. The contents of the control memory ICW locations are set by the operating programs. The NDRO entrance address is dependent upon the position of the BOOTSTRAP switch (0, 1, or 2). Then, the interrupt routine or bootstrap routine is executed. The interrupt subroutine is terminated by executing the *Interrupt Return* Instruction (code 07 5). Control is returned to the interrupted state by restoring (from control memory) the ASR and P values existing at the moment of interrupt.

**Multiple Interrupts** — An interrupt that has not been locked out may interrupt an operating

program even if the program is itself processing an interrupt. Interrupts may therefore be cascaded from Class IV to Class I or Class I to Class IV, or within a class, by clearing the appropriate lock-out designator in the ASR. Any interrupt analysis subroutine permitting such action within the same Class requires saving the Designator Storage Words for each interrupt.

**IOC Interrupts** — Two types of interrupts may result from IOC activity. Abnormal internal interrupts are generated by the IOC whenever the:

- inter-computer time-out exceeds the optional 250, 500, 1000, 2000, or 4000 milliseconds allowed.

- IOC detects an illegal function code

- the IOC request to memory exceeds the allotted time

Normal internal interrupts are generated by the IOC whenever:

- a buffer transfer, with imposed monitor, terminates (*Input Data, Output Data, External Function or External Interrupt Monitor Interrupts*)

- the IOC monitor clock is loaded with zero (*IOC-Processor Interrupt*)

- the IOC monitor clock counts down through zero (*Monitor Clock Interrupt*)

## INPUT-OUTPUT CONTROLLER AND ADAPTER

The UYK-7 input-output controller contains the necessary control and timing circuitry to conduct orderly input and output transfers of data, external commands and external interrupts between accessible memory modules and the external devices on 4, 8, 12 or 16 full-duplex channels; and to update both the real-time clock register and an activated monitor clock register. IOC functions are governed by a chain of commands (input/output programs) initiated by one or more controlling central processors. Input/output programs define buffer areas, channel numbers, and any functions related to word or byte size, imposed monitors, and transfer types.

## Interface Adapter

The interface adapter module associated with each IOC contains interface circuitry for 4, 8, 12, or 16 input/output channels. This interface comprises output registers, line drivers, input amplifiers, and acknowledge timing. Options exercised in the available interface voltage levels (N3, N15 or P3.5, which are -3V, -15V, and +3.5V respectively) are supplied in the adapter.

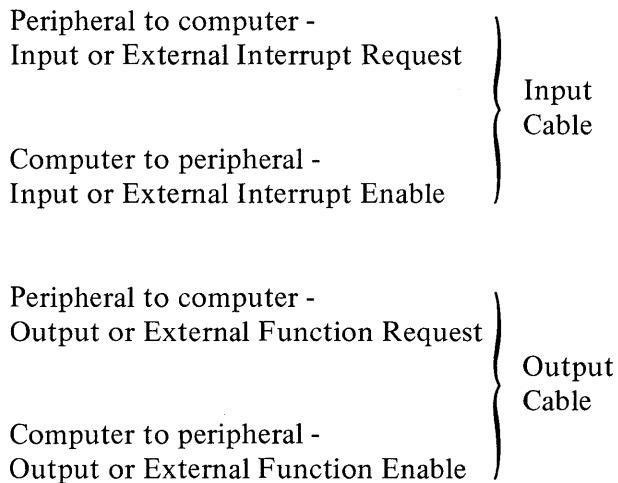

Number and characteristics of channels are provided in groups of four input and four output. Incoming data or control lines terminate in input amplifiers; each outgoing control line is driven by one line driver. However, the four output channels in each group share the 32 data line drivers; only one of the channels receives the associated control signal during the transfer. The channel interface lines for both an input and output parallel channel are shown in Figure 13.

Defined by easily-changed internal wiring, each channel can communicate in the following modes:

- Normal Buffer

- Externally Specified Index (ESI)

- Externally Specified Address (ESA)

- Inter-computer (IC)